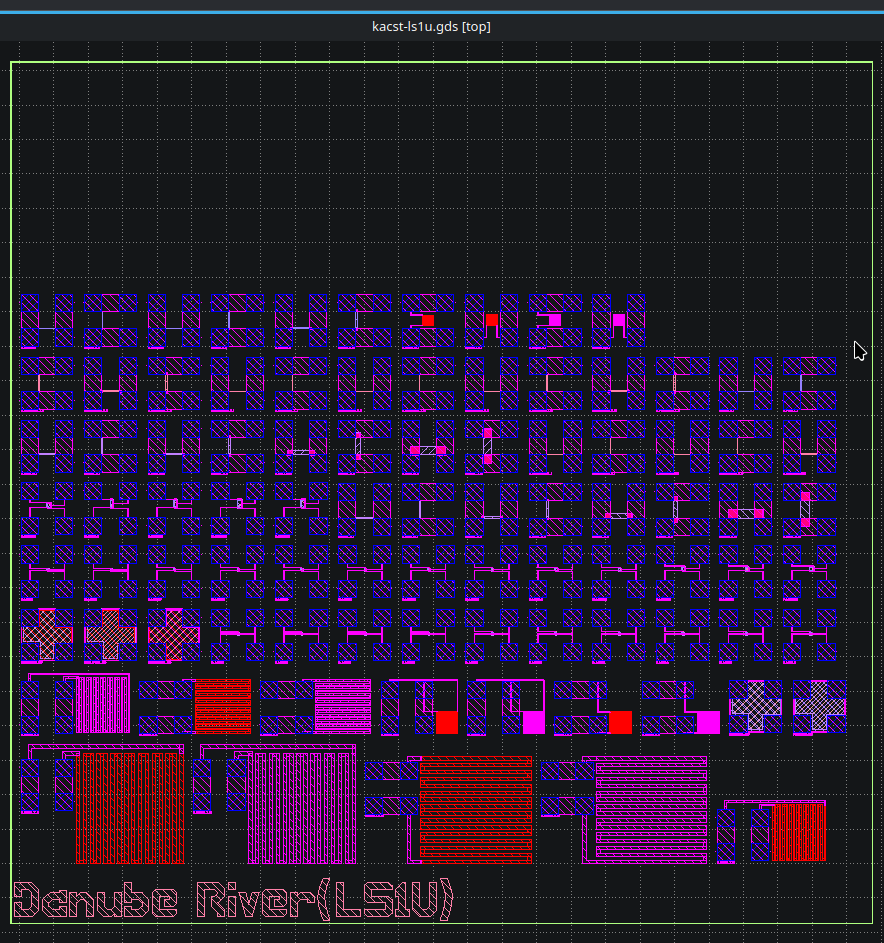

After more than a week of hacking, and a lot of cursing due to so much having changed in GDS Factory in the last year, I finally have Danube River work properly again.

I even finally got around and updated the wiki page and fixed some open bugs which have been open for a year now.

Besides finally properly stating the expected area size of the capacitors in the PDF also, instead of only in the CSV, I now also have more infos about the pin assignment and how to measure it in the exported PDF.

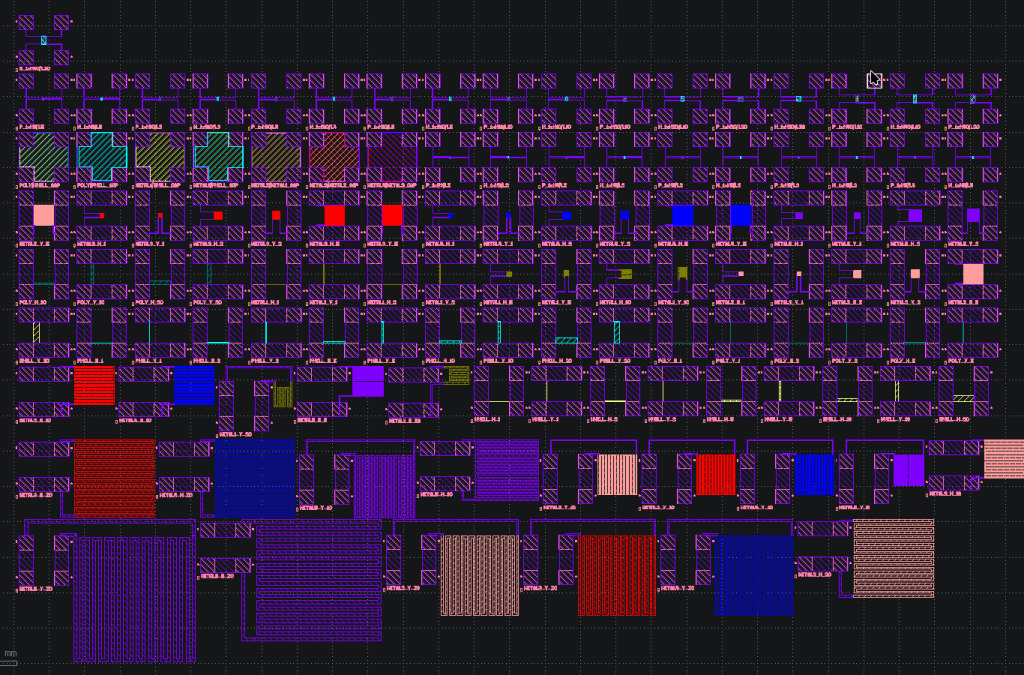

It’s really annoying that while GDS Factory broke Danube River with all their changes, their basic components still aren’t really very useful when it comes to auto-generating my circuits for the project I had to bring LibrePDK back up to speed for.

I’ve considered using GDSPy only but unfortunately I require some of the facilitation tools they’re providing like a proper snap to grid function and so.

At least I got around updating the wiki page for the Libre Silicon Stack now, and there’s now finally a page for the LibrePDK

Next step now is to get the Standard Cell Generator to spit out standard cells again.